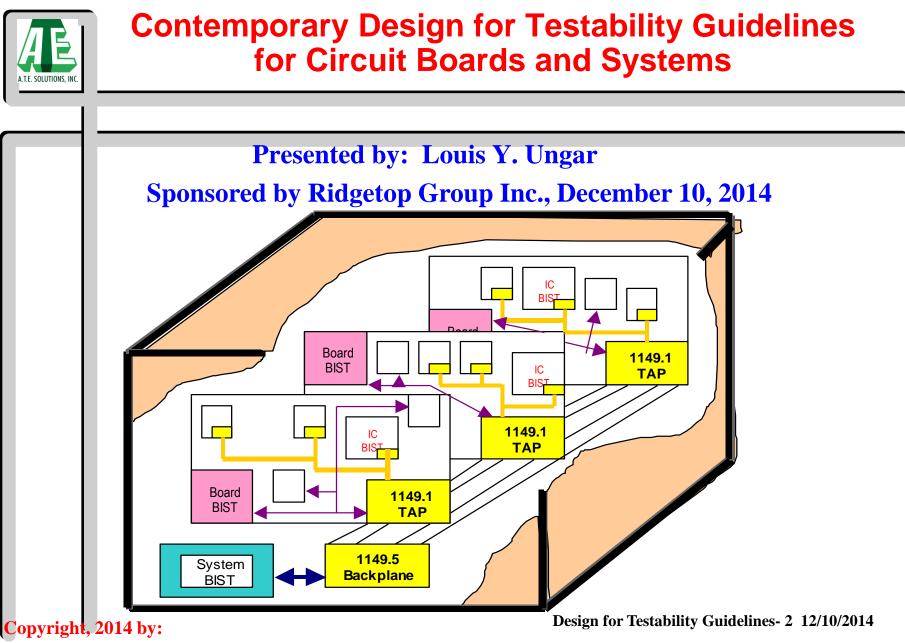

### **Contemporary Design for Testability Guidelines for Circuit Boards and Systems**

Louis Y. Ungar President Advanced Test Engineering Solutions Andrew Levy Vice President, Business Development Ridgetop Group

**December 10, 2014**

#### About the Presenter and Advanced Test Engineering (A.T.E.) Solutions, Inc.

Louis Y. Ungar

**Position** – President of A.T.E. Solutions, Inc., the leading testability consulting and educational firm

**Professional Associations** – President of the Testability Management Action Group (TMAG), Consultant to the American Society of Test Engineers (ASTE), SMTA Testability Committee, Member of the IEEE and IEEE Standards Balloting Committee for IEEE-1149.1-2013 & IEEE-1687.

**Major Accomplishments** – Educated nearly 10,000 test professionals from 2 dozen countries, consulted more than 100 organizations, created BestTest information source for test professionals, patents for Built-In Self Test, worked on DFT standards for SMTA, IEEE, IPC. Created The Test Flow Simulator and The Testability Director, software packages...

**Education** – BS in Electronics Engineering and Computer Sciences from UCLA, completed course work for MA in Management

**Professional Goals** – Convince engineers and managers that product quality through better test is not only noble, but also cost-effective

Copyright, 2014 by:

Design for Testability Guidelines- 3 12/10/2014

Copyright, 2014 by: <u>A.T.E. Solutions, Inc.</u> Phone: (310) 822-5231 email: LouisUngar@ieee.org\_Web: www.BestTest.com

Copyright, 2014 by:

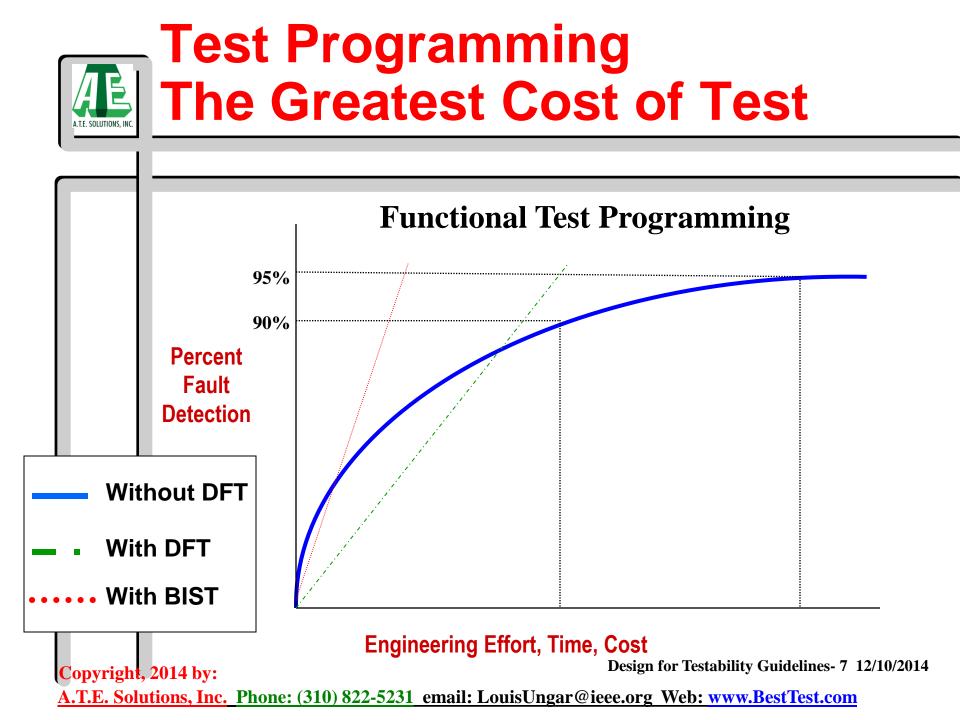

### WHAT IS DESIGN FOR TESTABILITY?

Design for Testability is a philosophy incorporated in the design of electronic circuits which takes into consideration the postdesign testing phase, and which attempts to reduce the effort and cost of testing.

#### **Testability = Controllability + Observability**

Design for Testability Guidelines- 5 12/10/2014

### MOTIVATIONS FOR TESTABLE DESIGNS

- Reduce Test And Support Costs

- Gain Higher Product Quality Through Better Test

- Test Earlier And Improve Time To Market

Copyright, 2014 by:

Design for Testability Guidelines- 6 12/10/2014

#### The Most Important Testability Guidelines: When DFT Analysis is Performed and by Whom?

• When?

At conceptual design stage

#### During preliminary design stage

» Block diagram

Several times during detailed design and before design release

#### • Who?

DFT Analysis can be performed by designers, test engineers and testability engineers.

Trade-off analyses between various options should involve management.

Actual design changes must be made by designers

Design for Testability Guidelines- 8 12/10/2014

Copyright, 2014 by:

Copyright, 2014 by:

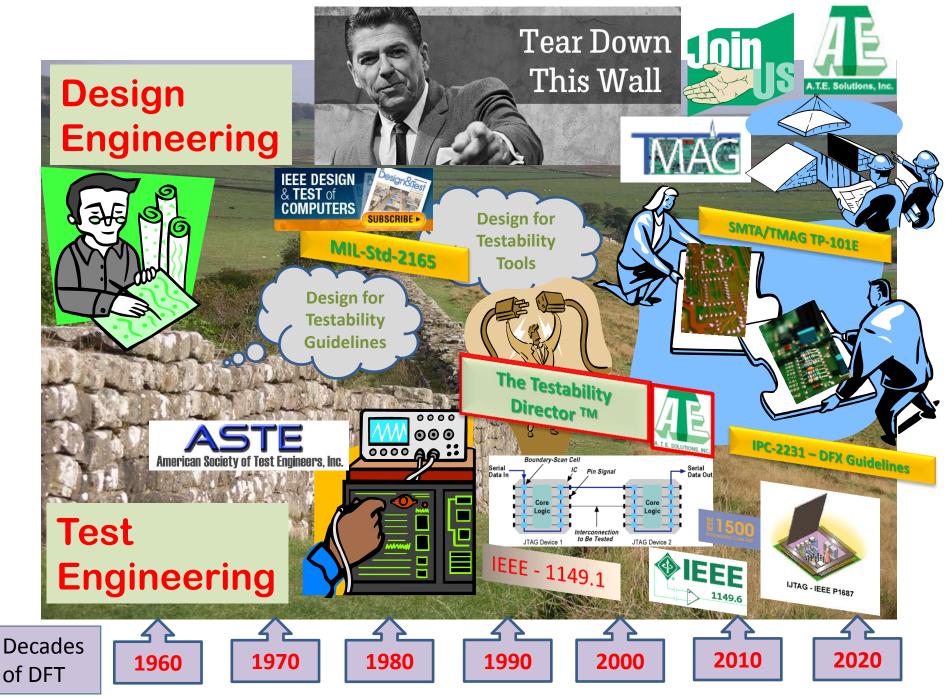

# **DFT Guidelines and Standards**

Design for Testability Guidelines- 9 12/10/2014

Copyright 2014, A.T.E. Solutions, Inc. All rights reserved

Copyright, 2014 by:

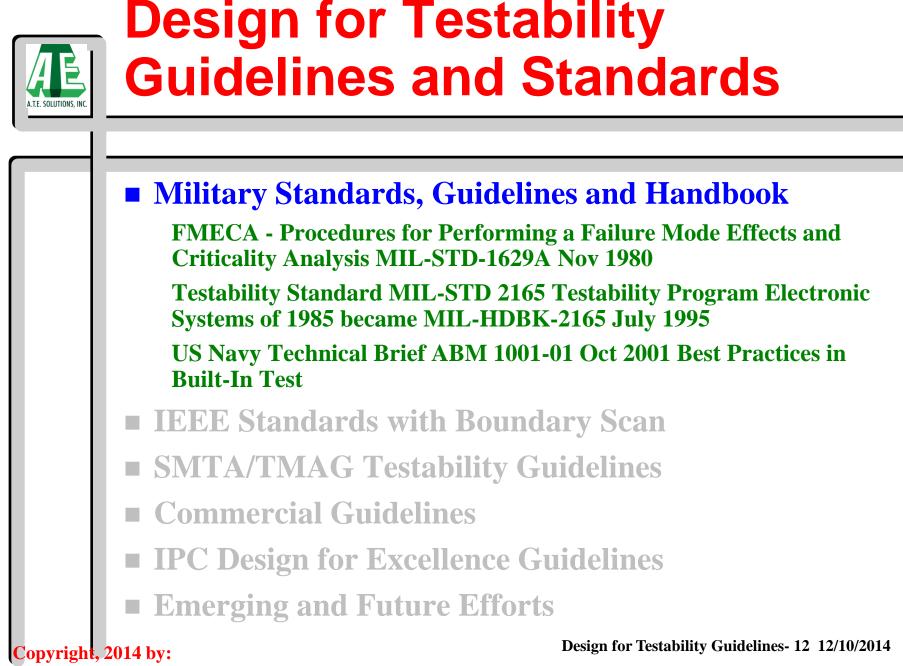

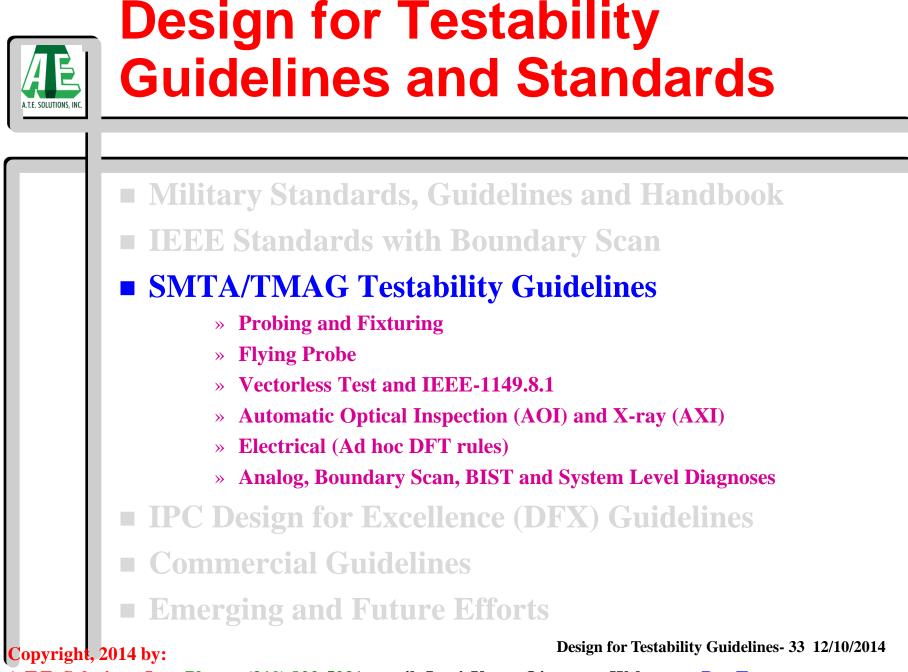

### **Design for Testability Guidelines and Standards**

- Military Standards, Guidelines and Handbook

- IEEE Standards with Boundary Scan

- **SMTA/TMAG Testability Guidelines**

- **Including probing and fixturing guidelines as well as "inspectability" for Automatic Optical Inspection and X-ray**

- Commercial Guidelines

- For sale software and free guidelines from tool makers

- IPC Design for Excellence (DFX) Guidelines

- Emerging and Future Efforts

Design for Testability Guidelines- 11 12/10/2014

Copyright, 2014 by:

### MIL-STD-1629A FME[C]A and Testability

- **FMEA is a great input to DFT Due early in design**

- FMEA provides important bases for Testability The number of failure modes identified provides a scope of how large the test will be

Each failure mode that has an effect implies detectability

- » No effect implies testability problem

- Multiple effects for a failure mode imply diagnosis issues

- » A single effect for a failure mode means perfect diagnosis Reliability and failure rate information in FMEA provides reliability weighting for both fault detection and isolation

IT IS CRUCIAL THAT FMEA BE PERFORMED EARLY IN THE DESIGN!

Design for Testability Guidelines- 13 12/10/2014

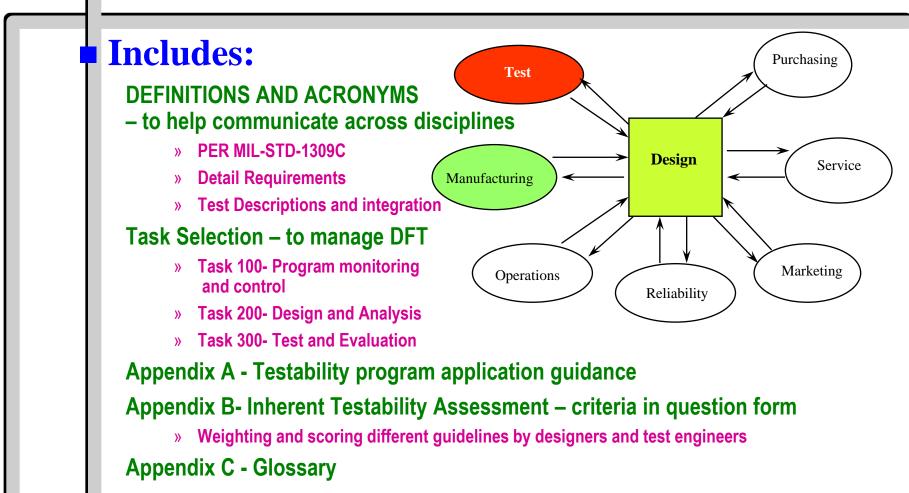

### MIL-HDBK-2165 Testability Standard

Copyright, 2014 by:

Design for Testability Guidelines- 14 12/10/2014

#### US Navy Technical Brief ABM 1001-01 Built-In Test Design and Optimization Guidelines

#### Purpose

To identify best practices in management, design and test in order to improve the reliability of fielded Built-In-Test (BIT) capabilities

#### Scope of BIT

Provides "built in" monitoring, fault detection and isolation capabilities as integral features of the system design.

BIT uses internal system hardware and software to test the system or its subsystems.

It often uses internal microprocessors and self-test software to isolate failures.

It can be supplemented with embedded "expert system" technology that incorporates diagnostic logic into the prime system.

» These supplemental capabilities should be used to address specific BIT deficiencies that cannot be effectively addressed via other means.

Copyright, 2014 by:

Design for Testability Guidelines- 15 12/10/2014

### **Design for Testability Guidelines and Standards**

- Military Standards, Guidelines and Handbook

- IEEE Standards with Boundary Scan

- **1149.1 Digital Boundary Scan**

- 1149.4 Mixed Signal Boundary Scan

- 1149.5 System Level Boundary Scan Dropped

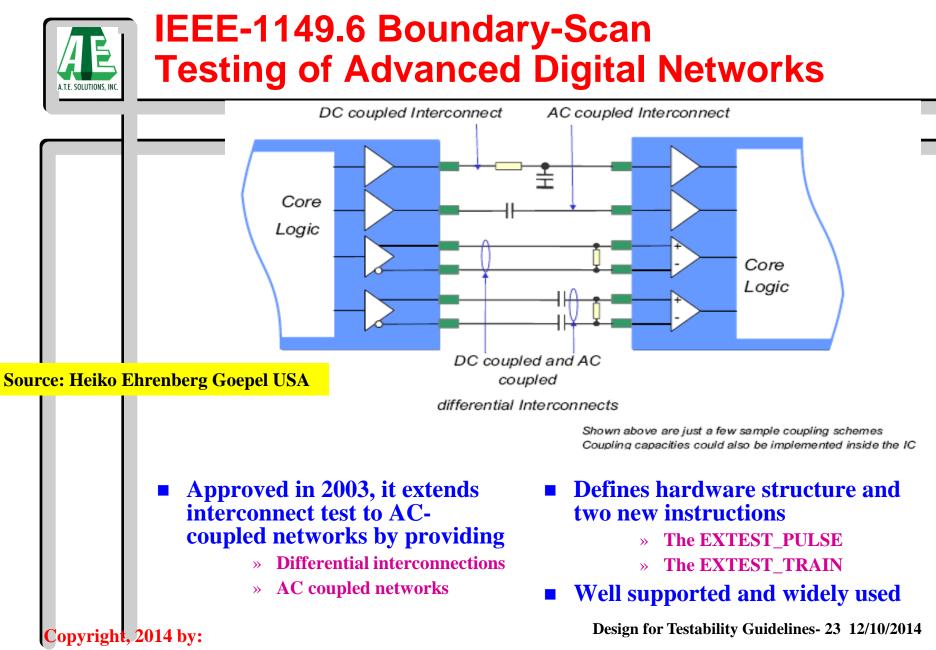

- 1149.6 Boundary Scan for Differential and AC Coupled Circuits

- 1149.7 2-pin Boundary Scan and Bulk Data Transfer

- 1500 Embedded Cores Accessed via Boundary Scan

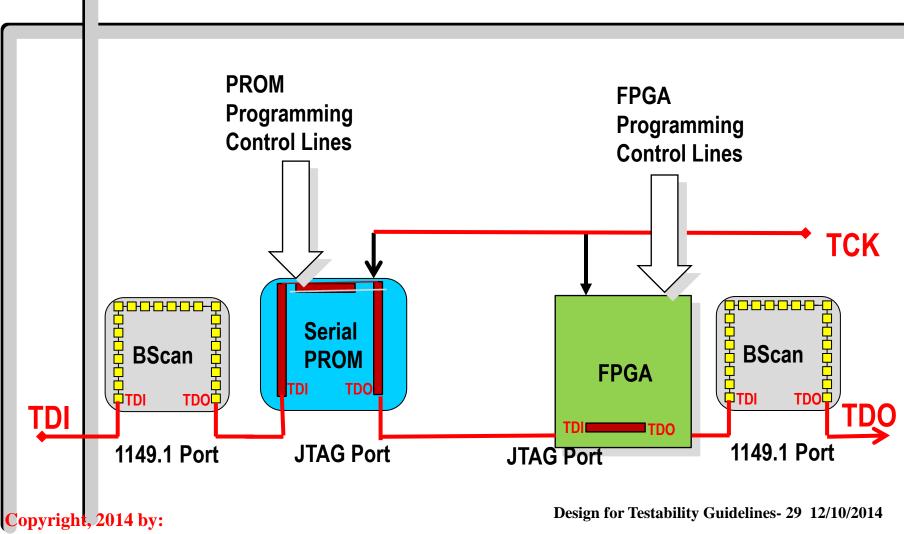

- **1532 Boundary Scan to program on-board programmable devices**

- **1581 Interconnects Boundary Scan with memory and provides protocol**

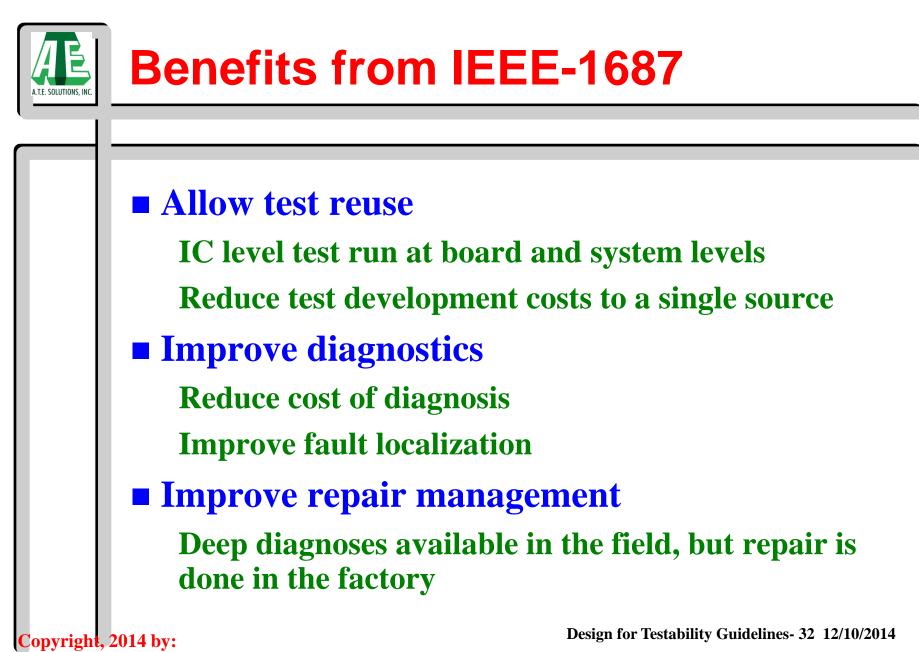

- **1687 Transports results of embedded test via Boundary Scan**

- SMTA/TMAG Testability Guidelines

- Commercial Guidelines

- IPC Design for Excellence (DFX) Guidelines

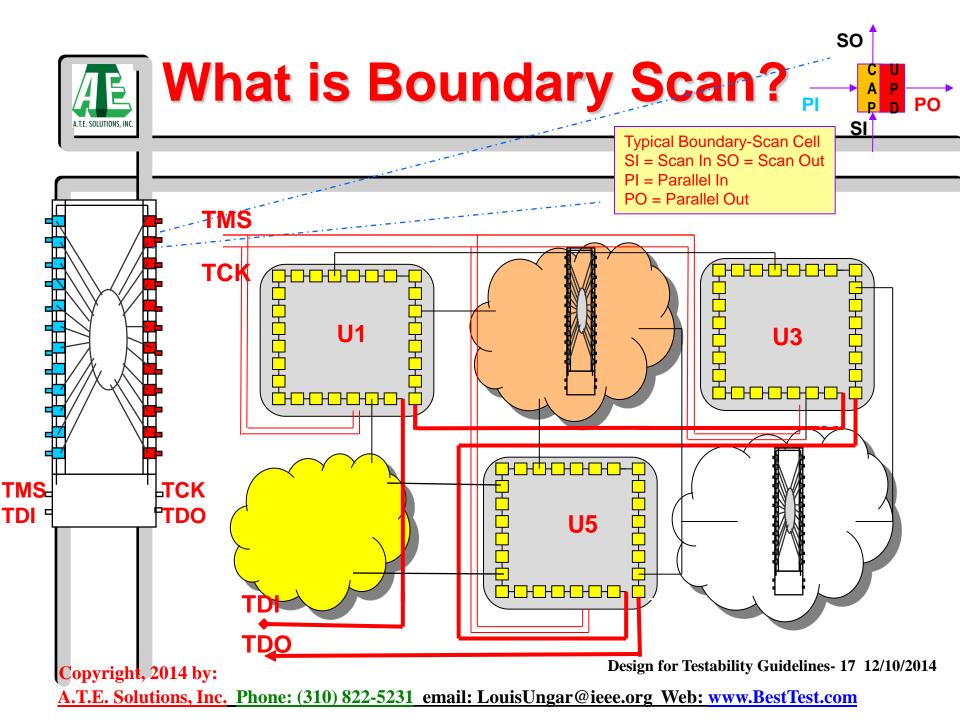

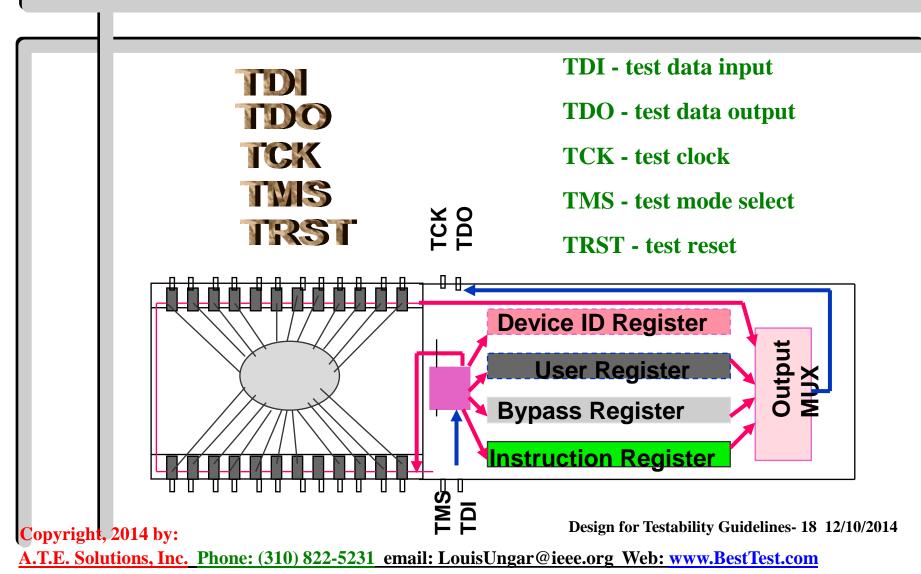

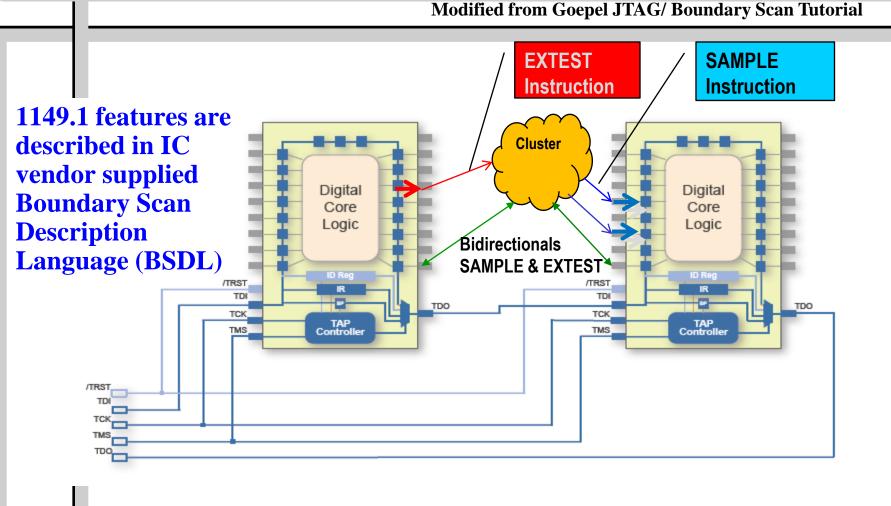

### **CONSTRUCTION OF THE 1149.1 TEST ACCESS PORT (TAP)**

# **1149.1 Boundary Scan Operation**

Copyright, 2014 by:

Design for Testability Guidelines- 19 12/10/2014

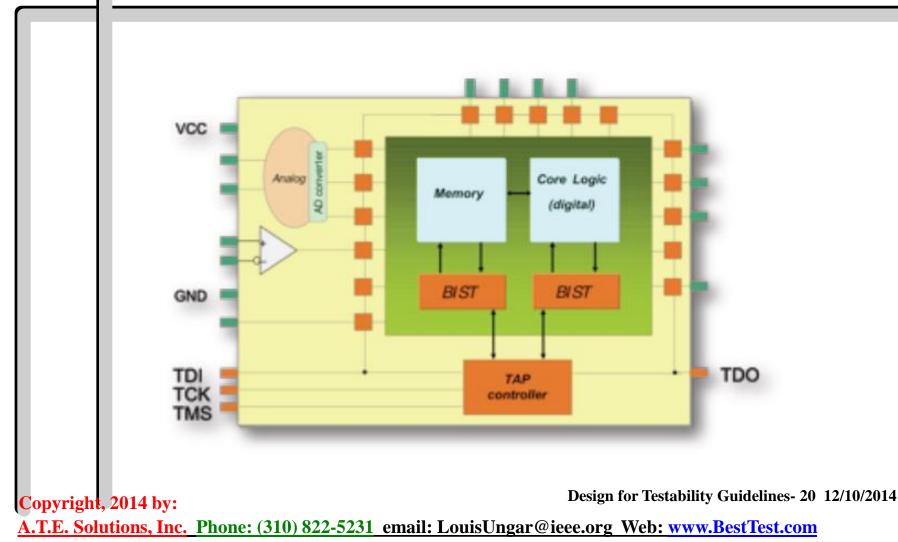

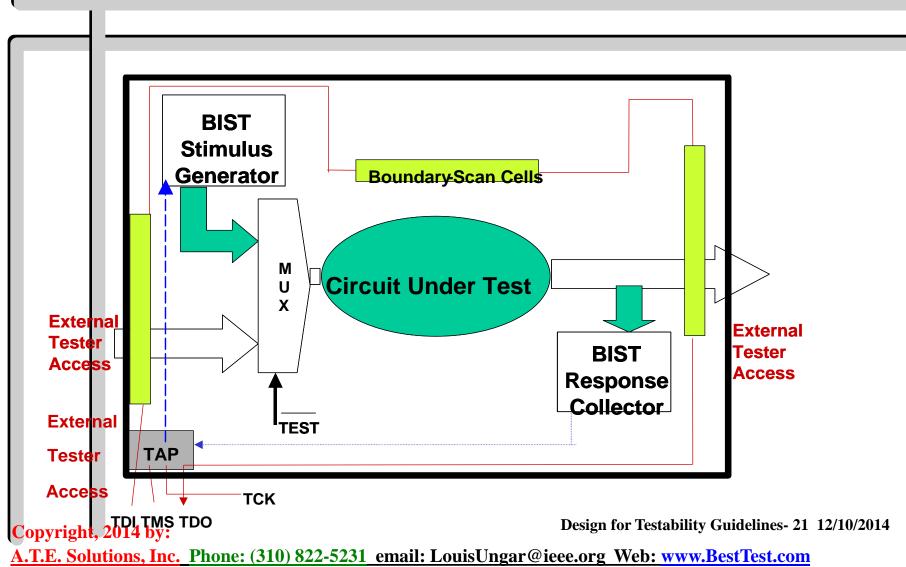

### IC Level BIST Controlled by Boundary Scan

Source: Goepel JTAG/ Boundary Scan Tutorial

# **Board Level BIST with Boundary Scan**

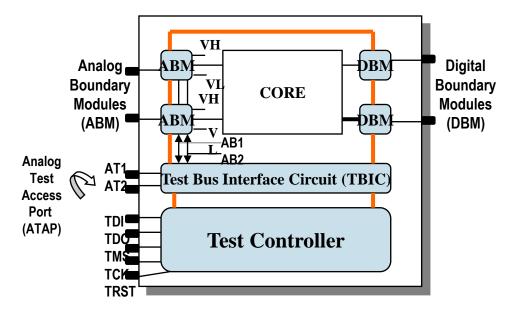

### IEEE 1149.4 - Mixed Signal Boundary Scan

- Approved as a full standard in 2001.

- Maintains the 1149.1 protocols, only adds analog capability.

- Still not in use...

Copyright, 2014 by:

Design for Testability Guidelines- 22 12/10/2014

Copyright, 2014 by:

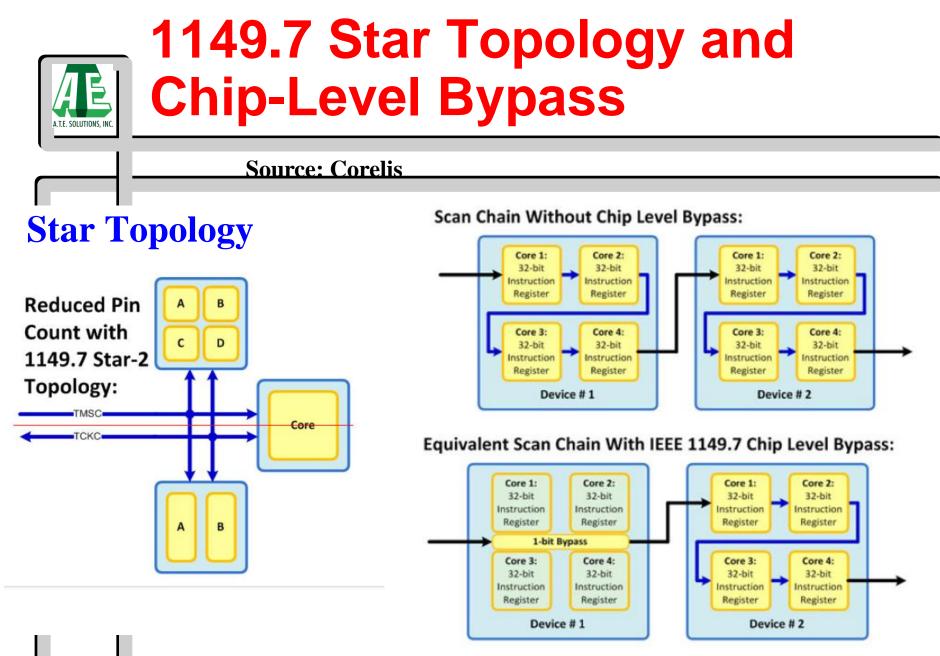

IEEE-1149.7 Reduced-pin and Enhancedfunctionality Test Access Port and Boundary Scan Architecture

#### Benefits:

#### **Reducing the number of pins**

» Only 2 pins needed for the TAP instead of 4 (or 5)

Improved support for devices with multiple cores

Increased debug performance

Major Features (besides lower pin count) Advanced power management features Star topology

Chip level bypass and Individual device addressing

Design for Testability Guidelines- 24 12/10/2014

Copyright, 2014 by:

Design for Testability Guidelines- 25 12/10/2014

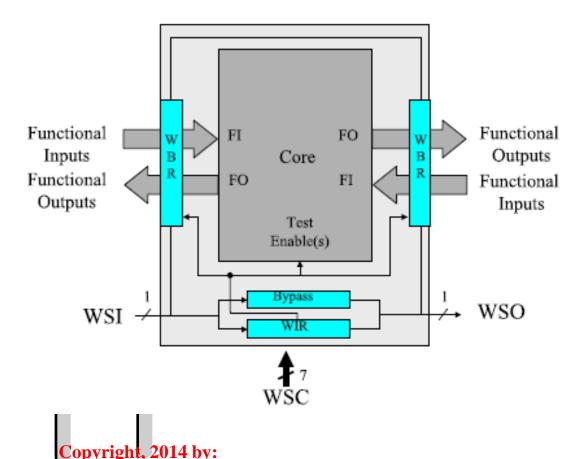

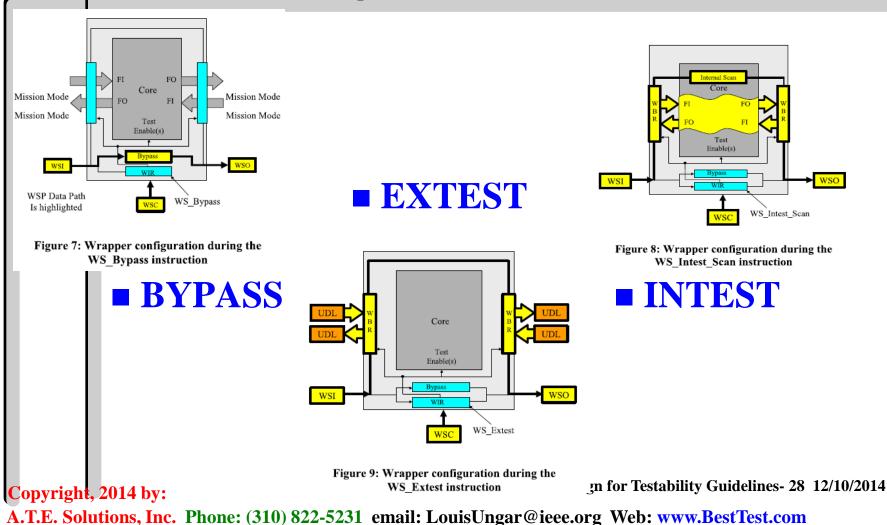

## IEEE-1500 Boundary Scan for System on Chip (SoC)

DaSilva, Zorian, Whetsel , Arabi, Kapur, Overview of the IEEE P1500 Standard , ITC 2003

A.T.F. SOLUTIONS, IN

Approved in 2005, the IEEE-1500 hardware architecture comprises

**Instruction Register**

Wrapper Instruction Register and two data registers

Wrapper Bypass Register (WBY)

Wrapper Boundary Register (WBR).

» The use of Core Data Registers (CDRs) is also anticipated by the standard.

Design for Testability Guidelines- 27 12/10/2014

# **IEEE-1500** Instructions

#### DaSilva, Zorian, Whetsel, Arabi, Kapur, Overview of the IEEE P1500 Standard, ITC 2003

#### IEEE 1532-2002 In-System Configuration of Programmable Devices Standard

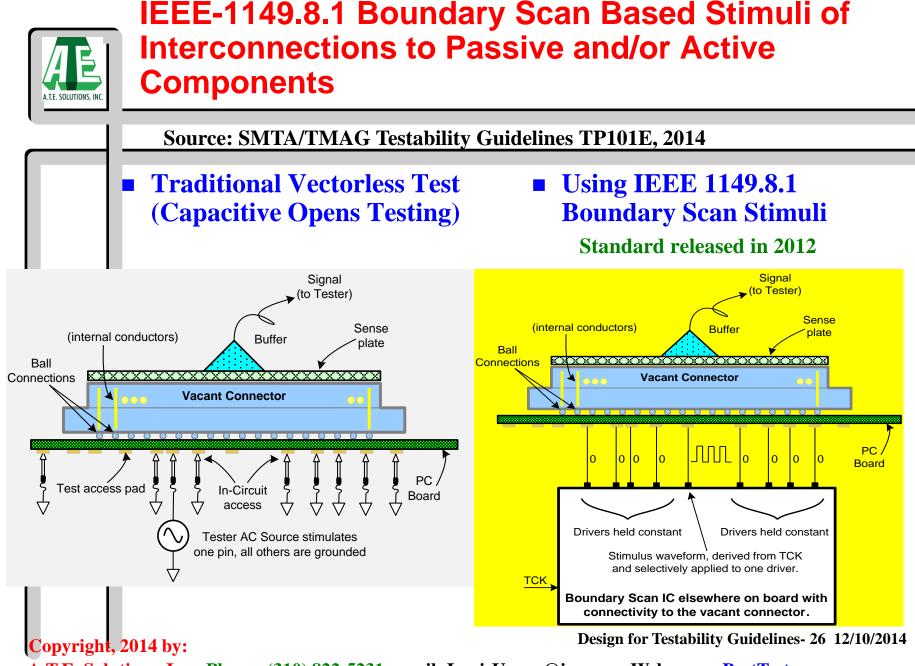

#### IEEE-1581 Static Component Interconnect Test Protocol and Architecture

- Approved in March 2011 it provides a means for a standard test methodology for memory interconnect testing.

- Describes test circuitry to be implemented in a memory device that bypasses the memory block itself and instead provides a logic connection between input and output pins (using simple logic gates).

- By stimulating the memory input pins and observing its output pins via boundary scan devices connected to the memory, board level connectivity can be verified.

Memory Ctrl. Memory Core P1581 Test Logic

Design for Testability Guidelines- 30 12/10/2014

Copyright, 2014 by:

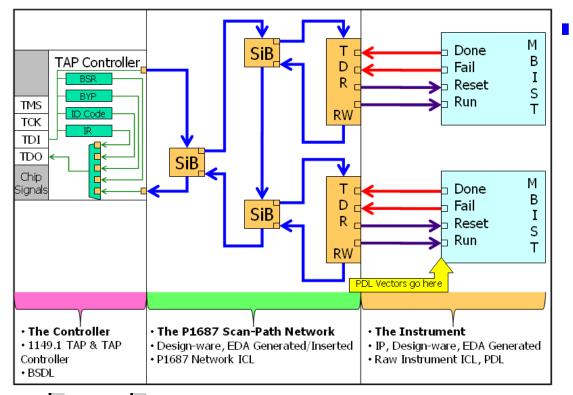

# **IEEE-1687** Architecture

#### From: Asset Intertech White Paper, 2013

# Internal JTAG (IJTAG) Standard for Embedded Instruments became a standard in 2014. Includes

A chip's boundary-scan TAP controller,

The device's internal IJTAG scan path network

Portable interface for the embedded instrument.

Segment Insertion Bit (SIB)

- » Acts as a gate

- » Allows on-demand access to instrument interface registers

Design for Testability Guidelines- 31 12/10/2014

Copyright, 2014 by:

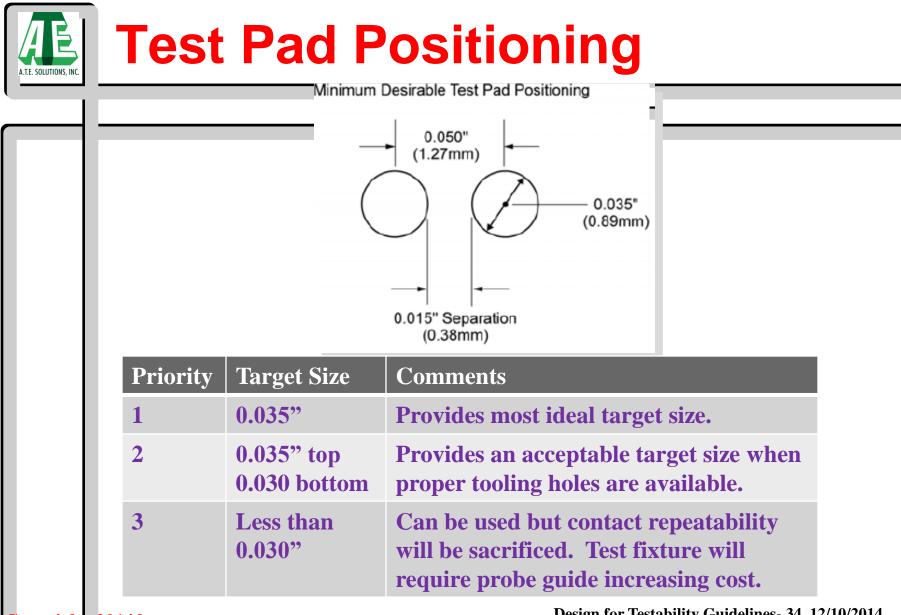

Source: SMTA/TMAG Testability Guidelines TP-101E

Copyright, 2014 by:

Design for Testability Guidelines- 34 12/10/2014

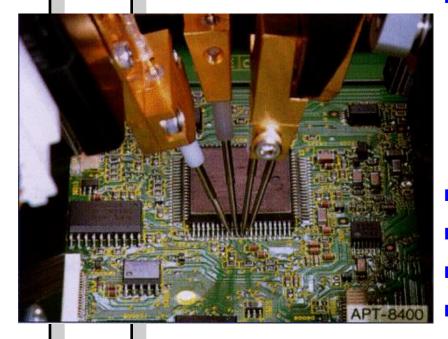

# **Flying Probe Testers**

Source: SMTA/TMAG Testability Guidelines TP-101E

Copyright, 2014 by:

- Flying probe testers can reliably hit test points with 0.025 in (0.64mm) diameters with 0.025 in. spacing.

- » Test vias and pads should be at least

0.014 in and have a 0.014 in free area,

and should be accessible from one side

of the board.

- Avoid probing large via holes

- Select the appropriate probe tip style

- Use board support to prevent flexing

- Optimize flying probe test times

- » e.g. Provide fixed access to large pin count nodes, such as ground and power nodes, on the PC board.

Design for Testability Guidelines- 35 12/10/2014

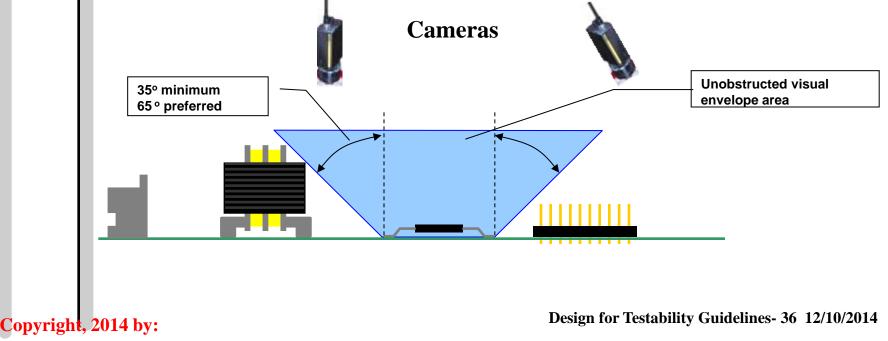

# Automated Optical Inspection (AOI) Guidelines

Source: SMTA/TMAG Testability Guidelines TP-101E

- Provides 18 "Design for Inspectability" Guidelines

- The combination of lighting and camera access requirements suggest an ideal 65-degree angle from vertical of unobstructed space.

- A minimum of 35 degrees is recommended when the full 65 degrees cannot be achieved.

### Minimize overlapping solder joints on double sided boards

Source: SMTA/TMAG Testability Guidelines TP-101E

**Cross-Section** Automatic X-ray Inspection (AXI)

#### Manual X-ray (MXI) **Uses Transmission X-ray**

Design for Testability Guidelines- 37 12/10/2014

## Design for Testability Guidelines and Standards

- Military Standards, Guidelines and Handbook

IEEE Standards with Boundary Scan

SMTA/TMAG Testability Guidelines

- **Commercial Guidelines (Several at IC level)**

IC Level - About a half dozen scan, DFT and ATPG vendors Boundary Scan – About a dozen Boundary Scan tool makers

**General Board Level** - ASTER's TestWay, others?

System Level - DSI's eXpress, QSI's TEAMS, others?

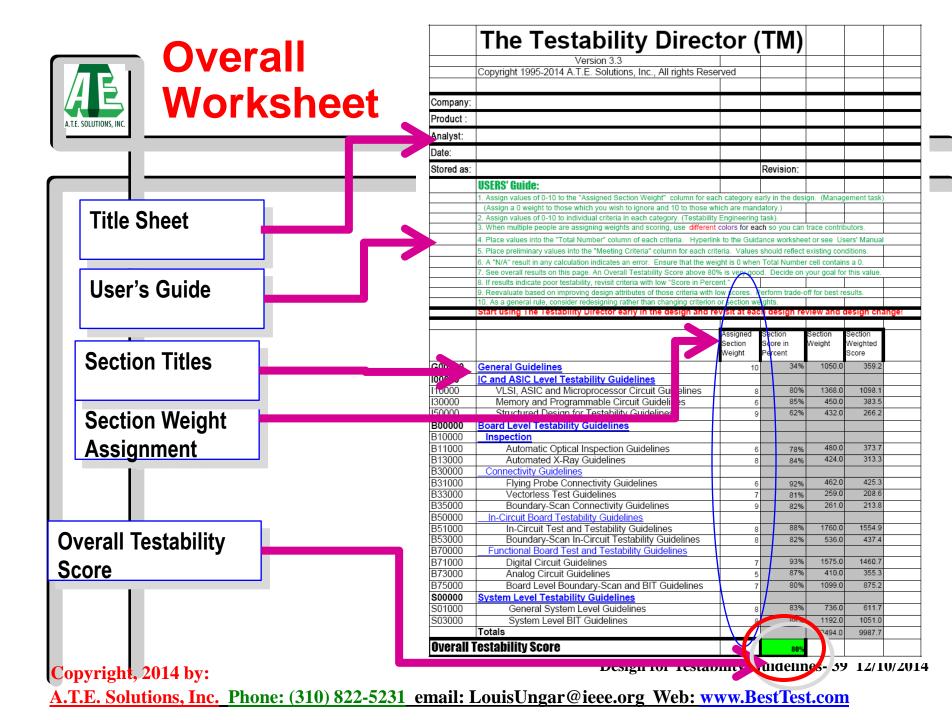

A.T.E. Solutions' The Testability Director <sup>TM</sup> includes hundreds of guidelines for ICs, Boards, Boundary Scan, System, Analog, BIST, etc.

IPC Design for Excellence (DFX) Guidelines

Copyright, 2014 by: <u>A.T.E. Solutions, Inc.</u> Phone: (310) 822-5231 email: LouisUngar@ieee.org Web: www.BestTest.com

## Where to Improve Testability

http://www.besttest.com/OurProducts/TestabilityDirector/

|          | eeds to<br>nprove!               |                                                     | The Testability Director                        | Assigned<br>Section |                                                  | Section<br>Score in | Section<br>Weight | Section<br>Weighted |  |  |  |

|----------|----------------------------------|-----------------------------------------------------|-------------------------------------------------|---------------------|--------------------------------------------------|---------------------|-------------------|---------------------|--|--|--|

| <u> </u> | •                                |                                                     |                                                 | Weight              |                                                  | Percent             | Voign             | Score               |  |  |  |

|          | G00000                           | 0 General Guidelines                                |                                                 |                     | 10                                               | 34%                 | 720.0             | 86.4                |  |  |  |

|          | B10000                           |                                                     | Board Level Inspection Guidelines               |                     |                                                  |                     |                   |                     |  |  |  |

|          | B11000                           |                                                     | Automatic Optical Inspection Guidelines         |                     | 6                                                | 78%                 | 480.0             | 373.7               |  |  |  |

|          | B13000                           | Automated X-Ray Guidelines                          |                                                 |                     | 8                                                | 86%                 | 320.0             | 240.5               |  |  |  |

|          | B50000                           | B50000 In-Circuit Board<br>Testability Guidelines   |                                                 |                     |                                                  |                     |                   |                     |  |  |  |

| B51000   |                                  |                                                     | In-Circuit Test and Testability Guidelines      |                     | 8                                                | 89%                 | 1712.0            | 1522.9              |  |  |  |

|          | B53000                           |                                                     | Boundary-Scan In-Circuit Testability Guidelines | (                   | 8                                                | 77%                 | 352.0             | 271.3               |  |  |  |

|          | B70000                           |                                                     | Functional Board Test and Testability Guidelin  | ies                 |                                                  |                     |                   |                     |  |  |  |

|          | B71000                           |                                                     | Digital Circuit Guidelines                      |                     | 7                                                | 93%                 | 1575.0            | 1460.7              |  |  |  |

|          | B73000 Analog Circuit Guidelines |                                                     |                                                 | 5                   | 88%                                              | 325.0               | 285.8             |                     |  |  |  |

|          | B75000                           | B75000 Board Level Boundary-Scan and BIT Guidelines |                                                 |                     | 7                                                | 88%                 | 630.0             | 552.4               |  |  |  |

|          | S00000                           |                                                     | System Level Testability Guidelines             |                     |                                                  |                     |                   |                     |  |  |  |

|          | S01000                           |                                                     | General System Level Guidelines                 |                     | 8                                                | 85%                 | 640.0             | 543.8               |  |  |  |

|          | S03000                           |                                                     | System Level BIT Guidelines                     |                     | 8                                                | 89%                 | 952.0             | 850.3               |  |  |  |

|          |                                  |                                                     | Overall Testability Score                       |                     | (                                                | 80%                 |                   |                     |  |  |  |

|          |                                  |                                                     |                                                 | Design for 7        | Design for Testability Guidelines- 40 12/10/2014 |                     |                   |                     |  |  |  |

Copyright, 2014 by:

Design for Testability Guidelines- 40 12/10/2014

### **General and Management Guidelines**

#### **General and Management Guidelines**

|                    |        |                                                                          |                      | _           |              |             |          |          |

|--------------------|--------|--------------------------------------------------------------------------|----------------------|-------------|--------------|-------------|----------|----------|

|                    |        |                                                                          | Criteria             | Tot         | al           | Meeting     | Score in | Weighted |

| Hyperlink criteria |        | Back to Overview and Overall                                             | Weight               | Nur         | mber         | Criteria    | Percent  | Score    |

| to extensive       | 01000  | General Guidelines                                                       | 1                    | 0           |              | $( \land )$ |          |          |

|                    | 010    | Are design requirements and specifications clearly documented prior      | /                    | 9           | 1/0          | 3           | 30%      | 27.0     |

| guidelines         |        | to the start of any design implimentation?                               |                      | $\Lambda$   |              |             |          |          |

| _                  | 01008  | Are DFT assessments made a part of design reviews at the beginning       |                      | 9           | 15           | 10          | 67%      | 60.      |

| Criteria Weight    |        | of conceptual_block diagram, and circuit design stages?                  |                      |             |              |             |          |          |

| assigned by Test   | )1010  | Is the entire development team aware of testability requirements?        |                      | 8           | 5            | 2           | 40%      | 32.      |

|                    | )1015  | Is a Failure Mode Effects (Criticality) Analysis being performed for     |                      | 9           | 15           | 10          | 67%      | 60.      |

|                    |        | each design milestone?                                                   |                      |             |              |             |          |          |

| Criteria scoring   | 01017  |                                                                          |                      | 6           | 100          | 75          | 75%      | 45.      |

| •                  | ,1011  | Are the test strategy and DFT interactively traded-off during the design |                      |             |              |             |          |          |

| determined by      | 1000   |                                                                          | $\square$            | 4           | 5            |             | 20%      | 8.       |

| designers          | )1020  | Is the test equipment and tester software to be used selected?           |                      | 4           | 3            |             |          |          |

|                    | G01030 | Is testability review a part of the design review?                       |                      | U           | 3            | 2           | 67%      | 66.      |

|                    | G01040 | Has a Level of Repair Analysis been accomplianed:                        |                      | 7           | 8            |             | 25%      | 17.      |

|                    | G01050 |                                                                          |                      | 8           | 100          |             | 10%      | 8.       |

| Find specific      |        | - or each maintenance level, has a doubted and a seen made for each item |                      |             |              |             |          |          |

| tems to improve!   |        | on now built-in test (BIT), automatic test equipment (ATE), and general  |                      |             |              |             |          |          |

| •                  |        | purpose test equipment will support fault detection and fault isolation? |                      |             |              |             |          |          |

|                    | 01060  | Is the planned degree of test automation consistent with the             |                      | 9           | 100          | 10          | 10%      | 9.0      |

|                    |        | capabilities of the maintenance technician?                              |                      | $\square$   | -            |             |          |          |

|                    | G01070 | Have testability objectives been determined?                             |                      | 9           | 100          | 10          |          | 9.       |

|                    | G01080 | Have restrictions been established in meeting testability objectives?    |                      | 8           | 100          | 10          | 10%      | 8.       |

|                    | G01090 | Is a complete design documentation available to test engineers in a      | $ \uparrow \uparrow$ | 9           | 100          | 1/0         | 10%      | 9.0      |

|                    |        | timely manner?                                                           |                      |             | $\backslash$ |             |          | J        |

|                    |        | Section Totals                                                           | 10                   | 5           |              | $\smile$    | 34%      | 359.     |

|                    |        | <br>Desig                                                                | n for T              | <u>beta</u> | hility       | Guideli     | nes- 41  | 12/10/2  |

Copyright, 2014 by:

Design for Testability Guidelines- 41 12/10/2014

Copyright, 2014 by:

## **Design for Testability Guidelines and Standards**

- Military Standards, Guidelines and Handbook

- IEEE Standards with Boundary Scan

- **SMTA/TMAG Testability Guidelines**

- Commercial Guidelines

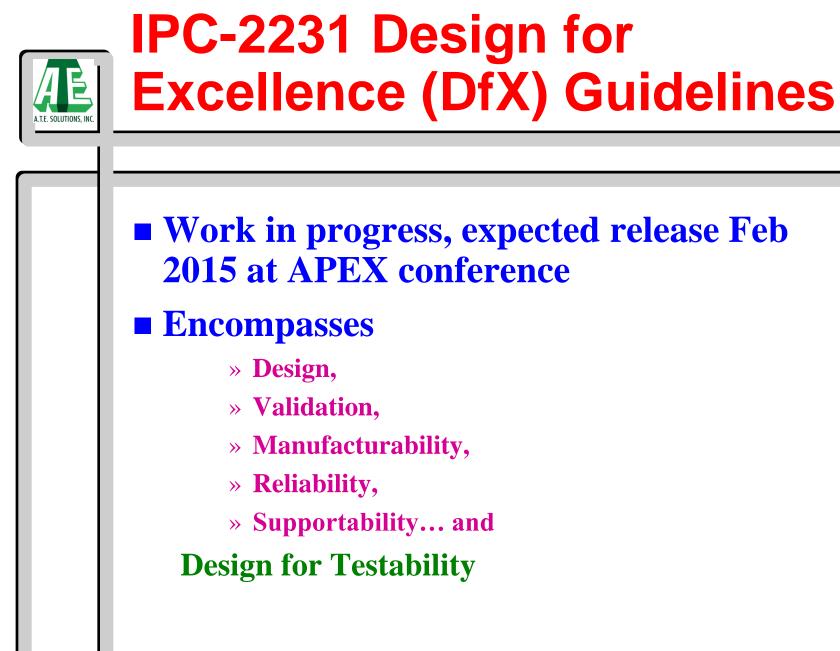

- IPC Design for Excellence (DFX) Guidelines

- Emerging and Future Efforts

Design for Testability Guidelines- 42 12/10/2014

Copyright, 2014 by:

Design for Testability Guidelines- 43 12/10/2014

| Development Phase                | Design Activity                                                                                                                          | Testability Activity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conceptual Design                | Create product specifications                                                                                                            | Create test requirements for each product specification, including fault detection, diagnosis, test times, test costs, etc.                                                                                                                                                                                                                                                                                                                                                                          |

| Block Diagram                    | Define partitions between blocks                                                                                                         | Ensure that all partitions are controllable and observable to all inspection<br>and test equipment considered. The mix of inspection and test equipment<br>stages should be determined and test resources identified and procured.                                                                                                                                                                                                                                                                   |

| Detailed Circuit<br>Design       | Electrical design of printed circuit<br>boards (PCBs), including<br>identification and procurement of<br>parts. Trade-off in components. | Ensure that parts with built-in test, such as boundary scan are given<br>preference. Ensure that controllability and observability within the circuit<br>are maintained. Ensure that "inspectability" for AOI and X-ray is<br>considered. Ensure that bed-of-nails, flying probe or boundary scan access<br>to all signals is available. All test program development can start here.                                                                                                                |

| Circuit Design<br>Verification   | Ensure circuit performs functions specified within tolerances and accuracies specified                                                   | Create and run design verification tests using discrete instruments or ATE.<br>(Note ATE is not necessary as test should only run once and the design<br>verification test is different manufacturing tests. The former looks for design<br>errors, the latter for defects. In some cases manufacturing tests can also<br>be used for field support tests.)<br>Environmental stress screening (ESS) such as HALT and HASS should be<br>performed here. To enable this, the product must be testable. |

| Manufacturing                    | PCB Layout                                                                                                                               | Circuit board accessibility issues need to be addressed to ensure sufficient access by the inspection and test equipment used in production.                                                                                                                                                                                                                                                                                                                                                         |

| Support                          | Field support and factory returns                                                                                                        | Ensure that tests developed for systems accurately identify failing<br>subsystems or parts that can be replaced quickly and easily by end user.<br>While manufacturing tests can be utilized once the product is returned to<br>the factory, field support tests typically utilize built-in test (BIT or BIST) to<br>repair by replacement. Design for BIT must take place as early as the<br>Block Diagram phase.                                                                                   |

| Prognosis<br>Copyright, 2014 by: | Product Health Management                                                                                                                | Ensure (during the Detailed Circuit Design phase) that there are sufficient monitoring points and mechanisms to ensure that (life critical) product degradations can be detected and diagnosed.                                                                                                                                                                                                                                                                                                      |

Copyright, 2014 by:

### **Design for Testability Guidelines and Standards**

- Military Standards, Guidelines and Handbook

- IEEE Standards with Boundary Scan

- **SMTA/TMAG Testability Guidelines**

- Commercial Guidelines

- IPC Design for Excellence (DFX) Guidelines

- Emerging and Future Efforts System Level – SJTAG DFT in 2020

Design for Testability Guidelines- 45 12/10/2014

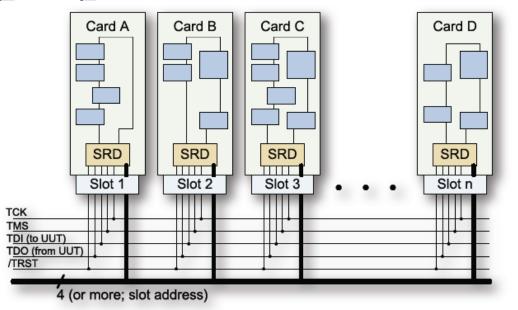

### SJTAG and System Level Boundary Scan Chain

Source: Goepel JTAG/ Boundary Scan Tutorial

#### **SJTAG**

Standardize data contents and formats for communication:

- » between external Test Manager platforms and internal Embedded Test Controllers

- eXternal Boundary Scan Test (XBST)

and

- » between Embedded Test Controllers and the UUTs they serve

- Embedded Boundary Scan Test (EBST)

Design for Testability Guidelines- 46 12/10/2014

Copyright, 2014 by:

## How will DFT change by 2020?

- Topics that will likely impact the future IDDQ Testing of CMOS (boards and systems)

SJ BIST from Ridgetop Group - Andrew Levy will cover this next Thermal Imaging for Diagnoses

Prognostic Health Management for all electronics

No Fault Found (NFF) and False Alarms > 70% of repairs

Overcome DFT & BIST security threats

Built-In Self Repair and Built-In Self Healing

- We'll keep you informed through our courses. <u>http://www.besttest.com/Courses/</u>

- We'll keep The Testability Director updated!

http://www.besttest.com/OurProducts/TestabilityDirector/

Copyright, 2014 by:

Design for Testability Guidelines- 47 12/10/2014

### **Existing Test Methods**

- Focus on Manufacturing Process

- Boundary Scan (JTAG / IEEE 1149.1)

- Optical / X-Ray Inspection

- Focus on Static Measurements

- Reliability Measurements Are Lacking

- Reliability = Performance over Time

- Implies field measurement & monitoring

- Intermittencies develop after deployment

Ridgetop Group 🛲

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

NZ,

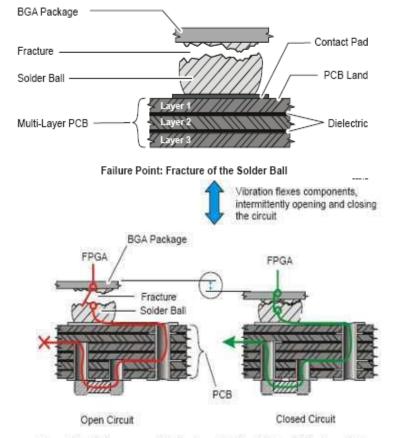

#### Intermittencies

- An interconnect intermittent fault is an event that causes the interconnect resistance to increase for a predefined amount and last for a minimum time.

- Fault detection is linked to # of occurences

- Definition evolved:

- From: R increase of  $1K\Omega$  lasting at least  $1\mu s$  $\rightarrow$  JEDEC 22-B111

- To: R increase of 200Ω lasting at least 200ns

- Interconnect is classified as failing if subsequent to the occurence of the first event, nine more events are detected that occur within a period of time T2 that is less than or equal to 10% of the time to the occurrence of the first event T1. (T2 <= 0.1\*T1)</li>

Ridgetop Group Inc.

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

#### Intermittencies

- With present technology, reported electronic system problems in the field cannot be duplicated at the service point or in the lab

- "Three/Four-letter" words (CND, NTF, RTOK)

- Could Not Duplicate (CND)

- No Trouble Found (NTF)

- Retest OK (RTOK)

- 50 to 80% of these CND/NTF/RTOK problem categories are reported by service personnel.

- Major culprits Solder joint intermittencies and NBTI effects in deep submicron ICs

Ridgetop Group Inc 3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

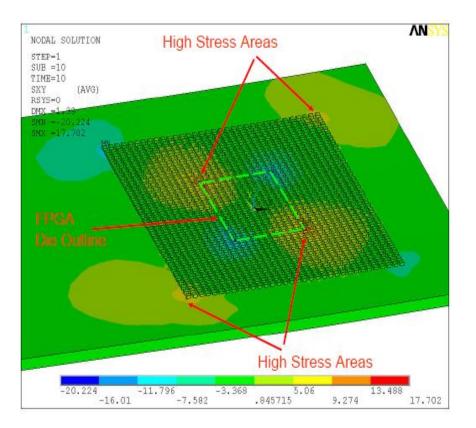

#### **Defects: Fractures & Intermittency**

**Ridgetop Group** Inc

Intermittent Failure caused by Fractured Solder Joint and Vibrational Stress

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

52

₩.

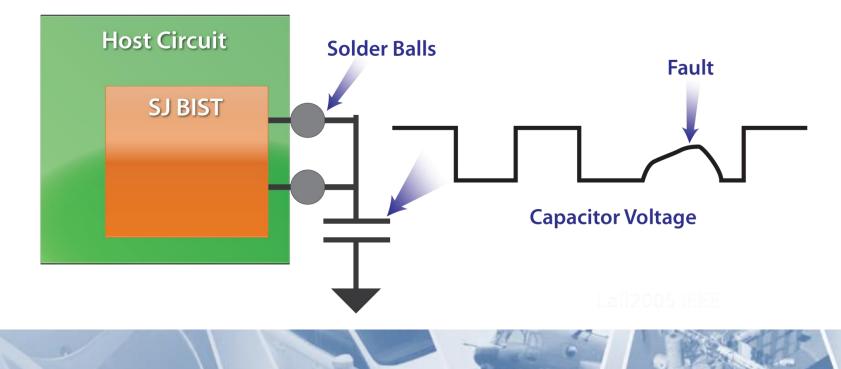

### SJ BIST™

- SJ BIST = Solder Joint Built-in Self-Test

- Verification & validation of solder joint interconnect reliability (Methodology applies any type of interconnection)

- Objectives

- Detection of impending interconnect failures

- Unique in-situ testing in operating circuits

- Technology-independent

- Features and Benefits

- Detects ball fractures prior to catastrophic failure of circuit

- Provides actionable maintenance data

- Independently tested and verified

- Endorsed by leading automotive and aerospace customers

- Also used for Highly Accelerated Life Test (HALT)

- Complements standard manufacturing test methods

Ridgetop Group Inc

**53**

NZ,

#### SJ BIST Operation

- Similar to a simple memory test: W0 R0; W1 R1

- Runs concurrently with host circuit

- Verilog/VHDL core (patent pending)

- Each core tests two I/O pins

- Pins are externally wired together

- Optionally small capacitor connected to the two pins

**Ridgetop Group** Inc

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

54

₩Ż.

### About Ridgetop Group, Inc.

- Incorporated in 2000, and headquartered in Tucson,

AZ. Ridgetop Europe established in 2010 in Belgium.

- Microelectronic Design and Test Solutions:

- SJ BIST<sup>™</sup> Based Test Solutions

- ProChek<sup>™</sup> Semiconductor Characterization System

- Q-Star Test<sup>™</sup> Precision Current Measurement Instruments

- PDKChek<sup>™</sup> In-Situ Test Structures

- ISO:9001/AS9100C-compliant Design and Integration Services

- Strong market position with commercial and government customers in USA, Canada, Europe, and Asia

**Ridgetop Group Facilities in Tucson, AZ**

Ridgetop Europe Facilities in Brugge, Belgium

Ridgetop Group me

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

#### **Questions?**

Slides and recording of the webinar will be available shortly via an e-mail from Ridgetop

- E-mail follow-up questions & comments to

- Louis Ungar: <u>louisungar@ieee.org</u>

- Andrew Levy: <u>andrew.levy@ridgetopgroup.com</u>

- Please fill out our brief feedback survey at: <u>https://www.surveymonkey.com/s/RCFP27Y</u>

Ridgetop Group Inc 3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

# Thank you!

#### Ridgetop Group, Inc.

3580 West Ina Road Tucson, AZ 85741

**Ridgetop Group** Inc

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

₩.